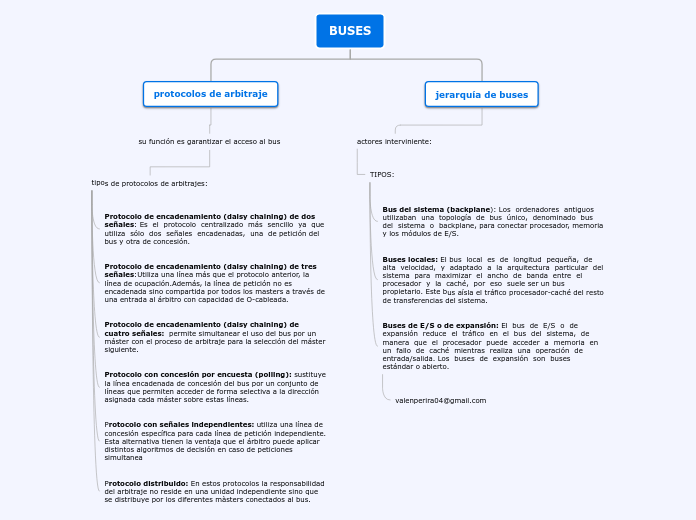

BUSES

protocolos de arbitraje

su función es garantizar el acceso al bus

tipos de protocolos de arbitrajes:

Protocolo de encadenamiento (daisy chaining) de dos señales: Es el protocolo centralizado más sencillo ya que utiliza sólo dos señales encadenadas, una de petición del bus y otra de concesión.

Protocolo de encadenamiento (daisy chaining) de tres señales:Utiliza una línea más que el protocolo anterior, la línea de ocupación.Además, la línea de petición no es encadenada sino compartida por todos los masters a través de una entrada al árbitro con capacidad de O-cableada.

Protocolo de encadenamiento (daisy chaining) de cuatro señales: permite simultanear el uso del bus por un máster con el proceso de arbitraje para la selección del máster siguiente.

Protocolo con concesión por encuesta (polling): sustituye la línea encadenada de concesión del bus por un conjunto de líneas que permiten acceder de forma selectiva a la dirección asignada cada máster sobre estas líneas.

Protocolo con señales independientes: utiliza una línea de concesión específica para cada línea de petición independiente. Esta alternativa tienen la ventaja que el árbitro puede aplicar distintos algoritmos de decisión en caso de peticiones simultanea

Protocolo distribuido: En estos protocolos la responsabilidad del arbitraje no reside en una unidad independiente sino que se distribuye por los diferentes màsters conectados al bus.

jerarquía de buses

actores interviniente:

TIPOS:

Bus del sistema (backplane): Los ordenadores antiguos utilizaban una topología de bus único, denominado bus del sistema o backplane, para conectar procesador, memoria y los módulos de E/S.

Buses locales: El bus local es de longitud pequeña, de alta velocidad, y adaptado a la arquitectura particular del sistema para maximizar el ancho de banda entre el procesador y la caché, por eso suele ser un bus propietario. Este bus aísla el tráfico procesador-caché del resto de transferencias del sistema.

Buses de E/S o de expansión: El bus de E/S o de expansión reduce el tráfico en el bus del sistema, de manera que el procesador puede acceder a memoria en un fallo de caché mientras realiza una operación de entrada/salida. Los buses de expansión son buses estándar o abierto.