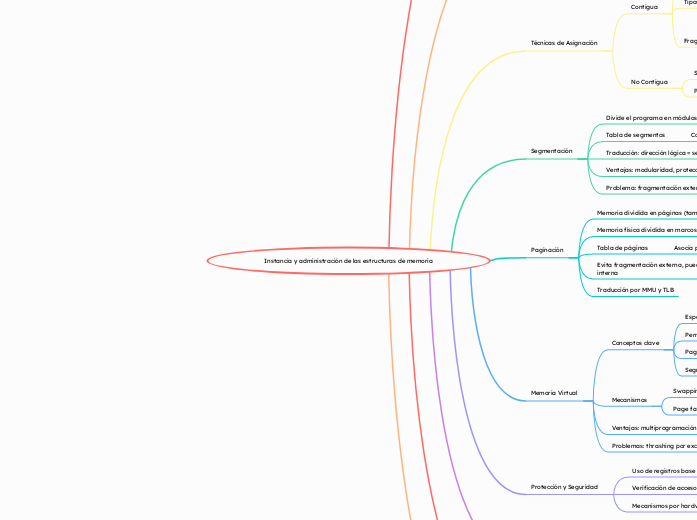

Instancia y administración de las estructuras de memoria

Memoria Principal

Definición: almacén de datos y programas en ejecución

Jerarquía de Memoria

Registros (más rápidos y pequeños)

Caché (rápido, cercano al CPU)

RAM (principal)

Disco (secundario)

Acceso: aleatorio (RAM), secuencial (cinta)

Temporalidad: volátil (RAM), no volátil (disco)

Objetivos de la Administración de Memoria

Asignación eficiente del espacio disponible

Protección entre procesos (aislamiento)

Permitir uso compartido seguro

Manejo lógico y físico de direcciones

Control y recuperación de espacio libre

Técnicas de Asignación

Contigua

Un solo bloque por proceso

Tipos de particiones

Fijas: tamaño predeterminado, fácil administración

Variables: tamaño adaptable, requiere compactación

Fragmentación

Interna: espacio no usado dentro del bloque

Externa: huecos entre bloques

No Contigua

Segmentación: bloques lógicos

Paginación: bloques físicos fijos

Segmentación

Divide el programa en módulos: código, datos, pila

Tabla de segmentos

Contiene base y límite de cada segmento

Traducción: dirección lógica = segmento + desplazamiento

Ventajas: modularidad, protección individual

Problema: fragmentación externa

Paginación

Memoria dividida en páginas (tamaño fijo)

Memoria física dividida en marcos

Tabla de páginas

Asocia páginas lógicas a marcos físicos

Evita fragmentación externa, puede causar fragmentación interna

Traducción por MMU y TLB

Memoria Virtual

Conceptos clave

Espacio lógico mayor que espacio físico

Permite ejecutar procesos grandes

Paginación bajo demanda

Segmentación bajo demanda

Mecanismos

Swapping: intercambio entre RAM y disco

Page fault: acceso a página no cargada

Ventajas: multiprogramación, aislamiento

Problemas: thrashing por exceso de intercambio

Protección y Seguridad

Uso de registros base y límite

Verificación de accesos con bits de control

Mecanismos por hardware y software

Optimización

Compactación: reorganización de memoria libre

Reubicación: mover procesos según disponibilidad

TLB: caché para traducción rápida de direcciones

Carga diferida: solo se carga lo necesario

Casos Prácticos

Cálculo de direcciones lógicas a físicas

Construcción de tablas de páginas

Simulación de fragmentación y swapping

Evaluación del uso de la memoria en distintos esquemas

Comparativa de Técnicas

Contigua: simple, rápida, fragmentación externa

Segmentación: lógica, modular, requiere tabla

Paginación: eficiente, requiere tabla y MMU

Virtual: flexible, puede provocar thrashing