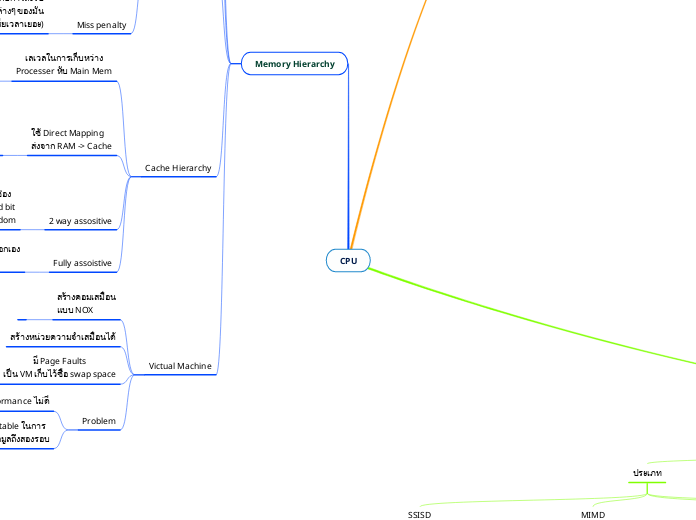

CPU

Single Processer

Central Processer Unit

Concept

ดึง -> ถอด -> คำนวน -> เก็บ

ทำงานตาม Clock Cycle

เก็บ Addres

อ่านคำสั่งว่าใช้ register อะไร ประเภทไหน

Logic Design Convention

1 รอบ & Cycle

ประมวลผลผ่าน Datapath

1. เก็บชุดคำสั่ง

เก็บคำสั่งรอการใช้และส่ง Address

2. Program Counter

เก็บ Address ถัดไป แล้วส่งคำสั่ง

3.Adder *แค่บวก

ทำการบวก

Datapath

หน่วยเก็บคำสั่งและข้อมูล

Register File

ดึงข้อมูลมา อ่าน เขียน จัดเก็บ ข้อมูลชั่วคราว

Register Write

คนคุม

ALU

ALU Operand

สั่งให้คำนวนอะไร

คำนวนทั้งตัวตัวเลขและตรรกะ

Branch

Taken = จริง

Not Taken = ไม่จริง ทำงานบรรทัดถัดไป

Sign-ex

แปลงข้อมูลขยายให้เป็น 32 bit เท่ากัน

Data Memory Unit

เก็บข้อมูลคำนวนแล้วใน ชุดคำสั่ง ข้อมูลต่างๆ

Memory Write

ตัวเขียนข้อมูล

Signal

ส่งคลื่คำสั่งมาบอก Memory Write

Machine Cycle (Pipeline)

ระบบการทำงาน

1.Fetch

ดึง Address จาก Memory

ข้อมูลการคำนวน

ชุดคำสั่ง

2.Decode

ถอดคำสั่งว่าต้องใช้คำสั่งอะไร

3.excute

ประมวลผลข้อมูล

4.writeback

เขียนกลับไปใน Register

5.Mem

เขียนกลับไปใน Memory

Pipeline Hazard

Structural

เป็นเพราะ Hardware

Data

เป็นเพราะใช้คำสั่งก่อนหน้า

มาเป็นผลลัพท์ในคำสั่งต่อไป

แก้ด้วย Forwarding / by Passing

เป็นเพราะ load-use

แก้ด้วย Bubble = ปล่อยมันไป

Control

เกิดจาก Check เงื่อนไขทั้งหมด

แล้วไม่รู้คำสั่งถัดไป

แก้ไม่ได้ เกิดบ่อยแต่ถ้าจะแก้

คือ Branch Prediction

เดาจากประวัติ และประมาณ %

Final State

Parrallel Processer

ประเภท

SSISD

Single อันแรกสุด

"ใช้คำสั่ง 1 คำสั่ง

แต่ทำหลายอย่าง"

ไม่เกิด Cache miss

ใช้ดีกับ For/Data Level Parallax

ไม่ดีกับ switch / case

MIMD

Muti / Cache Pallarial

ex . Quantum Comp

คล้ายกับ SSISD But Varity

ใช้ Vector กับ Scalar

Vector

(ดีกว่า)

เรียกครั้งเดียว

รู้ Pattern For Array

ใช้คำสั่งของมันจะไม่เจอ

Branch (if/else) = ไม่เจอ

Control Hazard

Scalar

เรียกทีละบรรทัด

ไม่รู้เลยโง่

SIMD

คำสั่งเดียว

ใช้ Data Stream หลายตัว

(ใช้ Vector register ให้คำสั่งต่อเนื่อง)

SPMD

Single Program

Muti Data

Hardware Muti-Tread

จำลอง CPU เสมือนกันสองตัว

และสลับผลัดกันใช้

Thread

มี Counter

บอกทำงานถึงไหน

สลับกันใน Core

Process

ทำสลับกับ OS

ทำงานช้า

การสลับ

ละเอียด

บังคับสลับกับ Thread

ทุกๆ Clock cycle

หยาบ

สลับตอนเกิด

Cache Miss

SMT

ตัวไหนพร้อมมาทำเลย

SMP

เก็บขึ้น Cloud

ใช้เก็บ Position ของ

Physical Mem

แชร์กันใช้ได้ทีเดียว

UMA

ส่ง Address

NUMA

เหมือนกันแต่

ต้อง Request

GPU

พัฒนาจากวงการเกม

GPU = Muti-Tread SIMD แต่ได้ result แบบ MIMD

ทำให้มี OpenCL , Vulcan

Subtopic

Nvdia มี CUDA สามารถ

เขียน Thread แบบ Low Level เลย

เป็นCPU ในปัจจุบัน ใช้แรมในการประมวลผลด้วย

Memory Hierarchy

การทำงาน

Temprial = ทำซ้ำๆ เช่น Loop

Special = ใช้ตัวที่เกี่ยวกับการเก็บข้อมูล

เหมือนมันเช่น Array,List,Collection,heep

Concept

ความลึก

ความหลายชั้น

ยิ่งใกล้ Pocessor

เก็บได้น้อย

ไวกว่าชั้นล่าง

แพง

ยิ่งไกล ยิ่งห่าง

เก็บได้มากขึ้นเรื่อยๆ

ลงไปช้าขึ้นเรื่อยๆ

Performance

Hit rate

hit = หาข้อมูลเจอในชั้นแรก

miss rate

หาข้อมูลไม่เจอในชั้นแรก

และต้องลงไปอีกชั้น

hit time

เวลาที่เสียไปกับการหาข้อมูลในชั้นเดียว

Miss penalty

เวลาที่เสียไปกับการลงไป

หาข้อมูลชั้นล่างๆ ของมัน

(ยิ่งเยอะ ยิ่งเสียเวลาเยอะ)

Cache Hierarchy

เลเวลในการเก็บหว่าง

Processer หับ Main Mem

มี Pagetable

เก็บการทำงานของโปรแกรง

ใช้ Direct Mapping

ส่งจาก RAM -> Cache

ใช้วิธีการจับคู่ข้อมูล โดน/ไม่โดน

โดยการเช็ค 2 อย่างนี้

Tags = เลข สองตัวหน้า _ _

บอกว่ามาจากไหนของแรม

เช็คว่าถูกมั้ย

Valid bit = ข้อมูลใน Cache

เป็นตัวที่ต้องการมั้ย

2 way assositive

คือการที่ Cache ช่องนึงมีสองช่อง

00,01 โดยดูจากเลขท้าย Valid bit

ว่าเป็น 0 หรือ 1 ด้วยการ Random

Fully assoistive

เป็นแบบใส่ช่องไหนก็ได้เราเลือกเอง

ทำเหมือน 2 way อิสระมาก

Victual Machine

สร้างคอมเสมือน

แบบ NOX

สร้างหน่วยความจำเสมือนได้

มี Page Faults

เป็น VM เก็บไว้ชื่อ swap space

Problem

Preformance ไม่ดี

ใช้ Pagetable ในการ

เข้าถึงข้อมูลถึงสองรอบ