によって Nicolaz Junco Chaparro 4年前.

1010

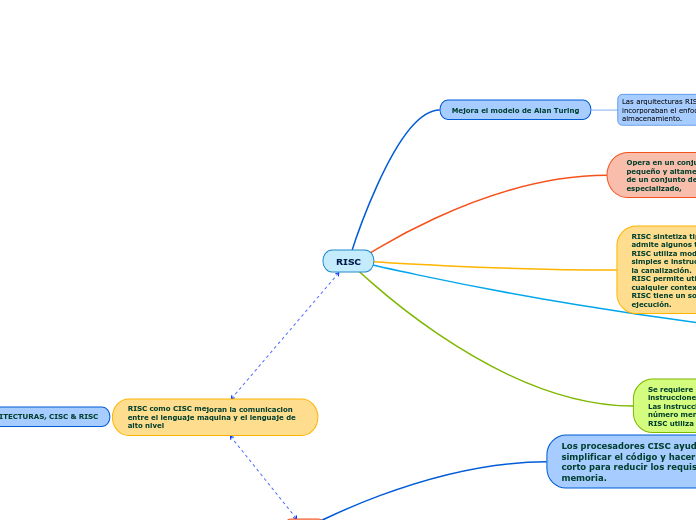

RISC

Los procesadores CISC fueron diseñados para simplificar el código y reducir los requisitos de memoria, introduciéndose en la década de 1970 para uso en dispositivos electrónicos simples como calculadoras y videojuegos.