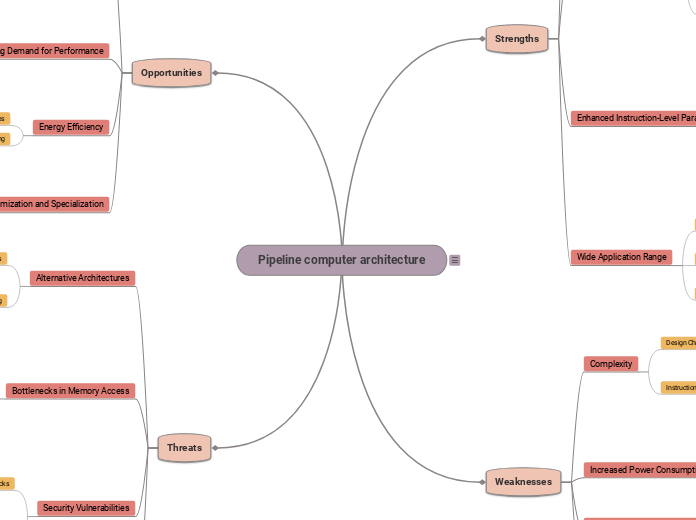

Pipeline computer architecture

Note: This SWOT analysis provides a comprehensive outline for assessing the strengths, weaknesses, opportunities, and threats associated with pipeline computer architecture. It is essential to conduct further research and analysis to gather specific information relevant to your context and industry.

Threats

Economic Factors

Market Competition

reducing the demand for pipeline architectures

Other architectures and technologies may gain market dominance

Cost-Effectiveness

Security Vulnerabilities

Side-Channel Attacks

making pipeline architectures more vulnerable to side-channel attacks

Caches and pipelines can leak information

Spectre and Meltdown-like Attacks

compromising system security

Pipeline architectures may be susceptible to speculative execution attacks

Bottlenecks in Memory Access

Memory Bandwidth

hindering performance

Insufficient memory bandwidth can bottleneck data transfer to and from the pipeline

Memory Latency

reducing overall performance

High memory access latencies can limit the advantages of pipeline architectures

Alternative Architectures

Vector Processing

challenging pipeline architectures

Specialized vector processors can provide superior performance for certain tasks

Superscalar Architectures

Opportunities

Customization and Specialization

Custom Accelerators

Domain-Specific Architectures

improving overall performance

Pipeline architectures can be tailored to specific application domains

Energy Efficiency

Green Computing

Low-Power Devices

Increasing Demand for Performance

Artificial Intelligence and Machine Learning

meeting the demand for real-time inference

Pipeline architectures can accelerate AI and ML tasks

Big Data Processing

making pipeline architectures valuable

Growing volumes of data require faster processing capabilities

Technological Advancements

Emerging Memory Technologies

improving overall system performance

New memory technologies may enhance memory access speeds

Instruction Set Enhancements

Advanced Processors

making pipeline architectures more effective

Upcoming processor technologies can offer increased parallelism

Weaknesses

Cost

Hardware Complexity

increasing production costs

Pipeline architectures may require specialized hardware components

Development and Implementation

Limited Benefit for Serial Tasks

Overhead

Sequential Dependencies

Increased Power Consumption

Pipeline Stalls

Instruction Overlap

resulting in higher overall power consumption

Overlapping instructions consume additional power

Complexity

Instruction Hazards

or control hazards can decrease performance

data hazards

Pipeline stalls due to dependencies

Design Challenges

Strengths

Wide Application Range

Multimedia Processing

such as video encoding and decoding

Supports efficient processing of multimedia data

Real-Time Systems

High-Performance Computing

such as scientific simulations and data analysis

Well-suited for computationally intensive tasks

Enhanced Instruction-Level Parallelism

Speculative Execution

improving overall system efficiency

Predicts and executes instruction branches in advance

Overlapping of Operations

reducing idle time during instruction execution

Enables concurrent execution of operations

Instruction Dependency Handling

enhancing performance

Allows independent instructions to be executed simultaneously

Scalability and Flexibility

Support for Multiple Architectures

making it versatile

Can be implemented across various types of computer architectures

Increased Throughput

enhancing system scalability

Accommodates a higher number of instructions per unit of time

Modular Design

enabling customization and adaptability

Facilitates the addition or removal of pipeline stages

Improved Performance and Efficiency

Reduced Latency

resulting in faster processing speeds

Minimizes the time taken to execute instructions

Resource Utilization

Parallel Processing

enhancing overall system performance

Allows simultaneous execution of multiple instructions